iCE40 Communication Ring Test Notes

Dependencies

Install instructions for all of the above tools can be found on the IceStorm website.

Building

The default make target synthesizes the design and runs a timing analysis. The target prog programs an available iCEBreaker via USB.

Running

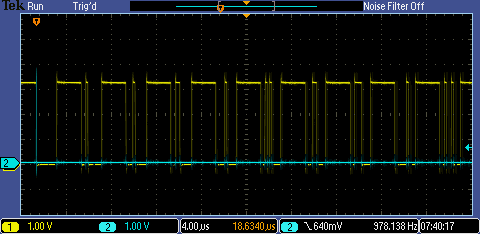

I used two iCEBreaker boards. Each board's P1A1 is connected to the other's P1A2. (If you connect the two P1A1 pins together, the drivers will fight each other until one burns out.) I monitored P1A4 on one of the boards with an oscilloscope. By triggering on this signal, I can time how long it takes to send 256 packets round trip. (The result of the test is thus the frequency the oscilloscope reports times 256.)

Results

The fastest I can clock the FPGA while passing icetime's analysis is 39.75MHz. This lets us use a baud rate of nearly 5Mbit (we want to use 8x oversampling when receiving data since the two FPGAs clocks aren't synchronized). At this speed, we see groups of 256 round trips happening at a rate of 978Hz. So overall this means the individual round trip frequency is 250kHz.

Out of curiosity, I tried running at 48MHz as well and it seemed to work. At 60MHz however it quickly drops a byte. So here it seems prudent to stay within icetime's limits.